If you are tracking the GPU industry and academia – there is a nice open-source GPU named MIAOW

An abstract architecture of this GPU looks as below:

https://www.nextplatform.com/wp-content/uploads/2015/08/MIAOW_Overview_slide.png

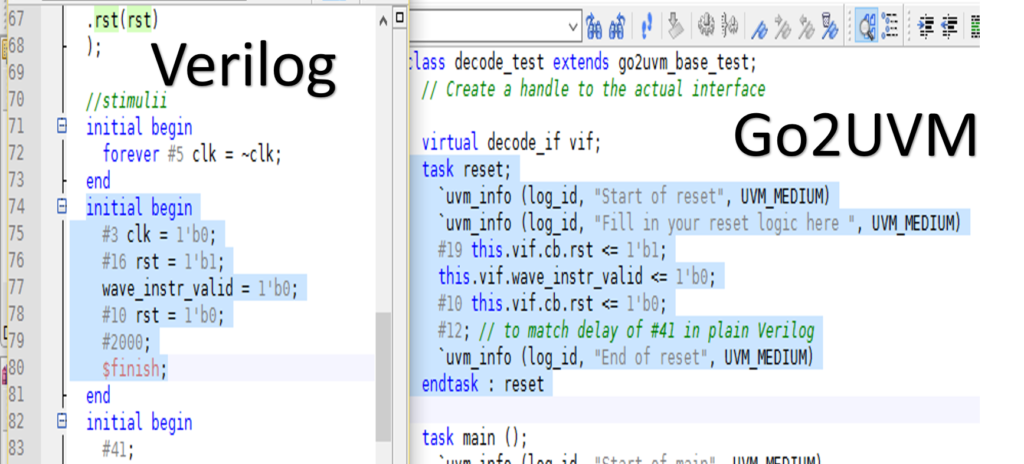

The design seems to be well structured and RTL coded nicely, organized well etc. However, as with many of these open-source hardware models that we find on the web, the verification with a testbench (simulation) is done in a loose manner. For instance we looked at the decode block in this GPU and the testbench is a simple Linear TB. We decided to port this to UVM via Go2UVM package to demonstrate how easy it really is to migrate to UVM from Verilog.

You can download the open-source GPU’s decode block and Go2UVM test from here:

On top of the recently released Go2UVM 2015.06 release, we added productivity “apps” to generate all the necessary code to get going with UVM in minutes – given a RTL. For instance we created a DVC_Go2UVM app that runs on popular Aldec’s Riviera-PRO simulator and generates Go2UVM infrastructure on a push-of-a-button. Specifically this app creates:

- SystemVerilog interface for the given RTL top module

- Top level TB module with DUT instantiated, connected

- Automates standard UVM run_test() mechanism to automate calling of components’ tasks (also known as Phasing in UVM)

- Creates a test.svi file that user can add the specific test scenario

Among these files the only file user needs to bother/tweak is the test.svi to capture necessary test sequence. In a typical RTL DUT, a testcase stimulus has 2 basic parts: RESET & MAIN. We managed to port the GPU’s decode tb to Go2UVM reset phase as below:

It is useful to appreciate that UVM automates calling of these tasks defined in a class based test provided we follow a standard naming convention – also known as Phasing in UVM. To get little deeper – with Go2UVM package, one does NOT have to bother about raising and dropping objections – the package does that for you! If you are new to this UVM objection mechanism, a good read is at: New to UVM? Wonder why it exits at time zero?

Now the main phase looks as below:

As one can appreciate – except for minor syntax changes, the original, plain Verilog Test and the corresponding UVM test with Go2UVM look very similar indeed!

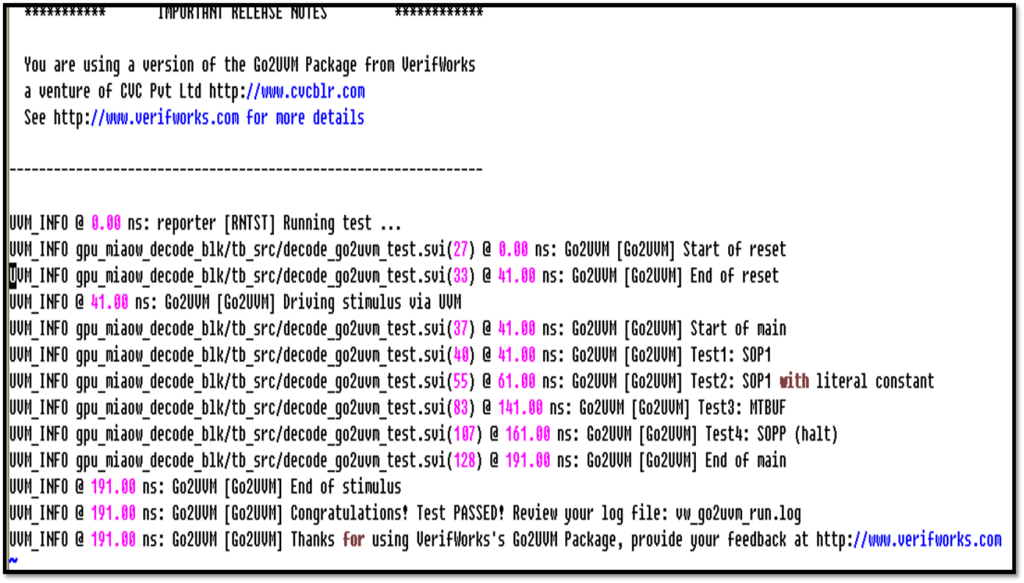

If you can start seeing the benefits of moving to UVM with Go2UVM – great, here is a treat for your eyes:

As you can see above, debugging with UVM becomes lot easier – as the file name, line number, time of the message etc. come out automatically in UVM!

You can download the open-source GPU’s decode block and Go2UVM test from here: